# CTU CAN FD IP CORE

# Datasheet

LOGIC DESIGN SERVICES I.t.d.

June 21, 2025

| O7-2018 Updated register map description, external references to generated maps. Update block diagrams. Updated test framework description. Updated Synthesis table.  2.1 10-2018 Added Register map block diagram after re-implementation of registers via Regist map generator.  12-2018 Added Register map block diagram after re-implementation of registers via Regist map generator.  12-2018 Added CRC Wrapper. Extended CRC description.  O1-2019 Added TIMESTAMP_LOW, TIMESTAMP_HIGH registers.  03-2019 Re-worked Prescaler. Removed 0x3 in bits 23:20 of address.  2.2 26-09-2019 Split functional description and register map from original document.  21-10-2019 Clarify TXT buffer behaviour when node goes bus-off.  31-10-2019 Clarify behaviour aftet Start-up. Clarify that frame must be inserted to TX Buffer before sending.  18-11-2019 Clarify behaviour of Transmitter delay measurement. Add notes on RX frame timestamping. Extend SSP position to 255.  13-12-2019 Clarify that only TEC above 255 will cause node to go Bus off.  30-4-2020 Add SETTING[PEX] and Protocol exception support.  28-10-2020 Add frame filters examples, add TBFBO and FDRF bits in SETTINGS registers, minor refactoring.  05-11-2020 Add general overview and TX frame type description.  4-2-2021 Add MODE[ROM] - Restricted operation mode.  4-2-2021 Add TXTB_INFO and mention generic number of TXT buffers.  39-4-2021 Add TXTB_INFO and mention generic number of TXT buffers.  Add RETR_CTR register.  Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer mode:  18-06-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer mode:  18-06-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer mode:  Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer mode:                                                                                                                                                  | Document<br>Version | Date       | Change description                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAN Core.  07-2018 Updated register map description, external references to generated maps. Update block diagrams. Updated test framework description. Updated Synthesis table.  2.1 10-2018 Added Register map block diagram after re-implementation of registers via Regist map generator.  12-2018 Added Register map block diagram after re-implementation of registers via Regist map generator.  12-2018 Added CRC Wrapper. Extended CRC description.  01-2019 Added TIMESTAMP_LOW, TIMESTAMP_HIGH registers.  03-2019 Re-worked Prescaler. Removed 0x3 in bits 23:20 of address.  2.2 26-09-2019 Split functional description and register map from original document.  21-10-2019 Clarify Bus-off behaviour aftet Start-up. Clarify that frame must be inserted to TX Buffer before sending.  18-11-2019 Clarify behaviour of Transmitter delay measurement. Add notes on RX frame timestamping. Extend SSP position to 255.  13-12-2019 Clarify that only TEC above 255 will cause node to go Bus off.  30-4-2020 Add SETTING[PEX] and Protocol exception support.  28-10-2020 Add frame filters examples, add TBFBO and FDRF bits in SETTINGS registers, minor refactoring.  05-11-2020 Add general overview and TX frame type description.  4-2-2021 Change license  23-2-2021 Add TXTB_INFO and mention generic number of TXT buffers.  4-2-2021 Add RETR_CTR register.  Add Reduce maximal number of bits on the fly during secondary sampling to 4.  29-05-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer moder.  11-06-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer moder.  18-06-2021 Add MODE[RXBAM] and COMMAND[RXRPMC] bits, describe RX buffer moder.  Add MODE[RXBAM] and COMMAND[RXRPMC] bits, describe RX buffer moder.  18-06-2021 Add MODE[RXBAM] and COMMAND[RXRPMC] bits, describe RX buffer moder.  27-6-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  Which allow flipping of CRC or Stuff count. | 1.0 07-2015         |            | Initial version describing release 1.0                                                                                                                                                                   |

| block diagrams. Updated test framework description. Updated Synthesis table.  2.1 10-2018 Added CR Synthesis table.  Added CR Wrapper. Extended CR description.  12-2018 Added CR Wrapper. Extended CR description.  01-2019 Added TIMESTAMP_LOW, TIMESTAMP_HIGH registers.  03-2019 Re-worked Prescaler. Removed Dx3 in bits 23:20 of address.  2.2 26-09-2019 Split functional description and register map from original document.  Clarify TXT buffer behaviour when node goes bus-off.  31-10-2019 Clarify Bus-off behaviour aftet Start-up. Clarify that frame must be inserted to TX Buffer before sending.  18-11-2019 Clarify behaviour of Transmitter delay measurement. Add notes on RX frame timestamping. Extend SSP position to 255.  13-12-2019 Clarify that only TEC above 255 will cause node to go Bus off.  30-4-2020 Add SETTING[PEX] and Protocol exception support.  28-10-2020 Add frame filters examples, add TBFBO and FDRF bits in SETTINGS registers, minor refactoring.  4-2-2021 Add MODE[ROM] - Restricted operation mode.  4-2-2021 Add MODE[ROM] - Restricted operation mode.  23-2-2021 Add TXTB_INFO and mention generic number of TXT buffers.  4-2-2021 Add STATUS[STCT] and STATUS[STRGS] bits.  26-0-5-2021 Add STATUS[STCT] and STATUS[STRGS] bits.  26-0-5-2021 Add STATUS[STCT] and STATUS[STRGS] bits.  26-0-5-2021 Add MODE[RXBM] and COMMAND[RXRRW] bits, describe RX buffer moder.  18-06-2021 Add MODE[RXBM] and COMMAND[RXRRW] bits, describe RX buffer moder.  18-06-2021 Add MODE[RXBM], MODE[SAM], STATUS[TXPE], STATUS[TXPE], COMMAND [CTPXE], and COMMAND[CTPXE]. Add FRAME_FORMAT_Within the short on party mechanism testif which allow dipinging of CR CO Stuff count. Add section on party mechanism testif which allow dipinging of CR CO Stuff count. Add section on party mechanism testif which allow dipinging of CR CO Stuff count. Add section on party mechanism testif share processed of CTU CAN FD. Bump document version accordingly.  5-7-2022 Add MODE[TXBBM], MODE[TXBBM] are automatically applied to "backup" TXT Buffers. Add reset_buffer_ams and a | 2.0                 | 09-2016    | Added test framework description. Updated document to cover latest description of CAN Core.                                                                                                              |

| 12-2018 Added Register map block diagram after re-implementation of registers via Regist map generator.  12-2018 Added CRC Wrapper. Extended CRC description.  01-2019 Added TIMESTAMP_LOW, TIMESTAMP_HIGH registers.  03-2019 Re-worked Prescaler. Removed 0x3 in bits 23:20 of address.  2.2 26-09-2019 Split functional description and register map from original document.  21-10-2019 Clarify TXT buffer behaviour when node goes bus-off.  31-10-2019 Clarify Bus-off behaviour aftet Start-up. Clarify that frame must be inserted to TX Buffer before sending.  18-11-2019 Clarify behaviour of Transmitter delay measurement. Add notes on RX frame timestamping. Extend SSP position to 255.  13-12-2019 Clarify that only TEC above 255 will cause node to go Bus off.  30-4-2020 Add SETTING[PEX] and Protocol exception support.  28-10-2020 Add frame filters examples, add TBFBO and FDRF bits in SETTINGS registers, minor refactoring.  05-11-2020 Add general overview and TX frame type description.  4-2-2021 Change license  2.3 4-2-2021 Added MODE[ROM] - Restricted operation mode.  23-2-2021 Add TXTB_INFO and mention generic number of TXT buffers.  9-4-2021 Add EETR_CTR register.  26-4-2021 Add STATUFS[STCNT] and STATUS[STRGS] bits.  26-05-2021 Add STATUFS[STCNT] and STATUS[STRGS] bits.  26-05-2021 Reduce maximal number of bits on the fly during secondary sampling to 4.  29-05-2021 Add MODE[TXBAM] and COMMAND[RXRPMV] bits, describe RX buffer mode:  18-06-2021 Add MODE[TXBAM] and COMMAND[RXRPMV] bits, describe RX buffer mode:  Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], CMMAND [CTPXE] and COMMAND[CRXPE]. STATUS[TXPE].  27-6-2022 Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], CMMAND [CTPXE] and COMMAND[CRXPE]. Add FRAME_FORMAT_W bit which allow flipping of CRC or Stuff count. Add section on parity mechanism testir.  27-6-2022 Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], CMMAND [CTPXE] and COMMAND[CRXPE]. SDATUS[TXPE].  28-6-2024 Add MODE[TXBBM], MODE[FXBM] are automatically applied to "backup" TXT Buffers. Add |                     | 07-2018    | Updated register map description, external references to generated maps. Updated block diagrams. Updated test framework description. Updated Synthesis table.                                            |

| map generator.  12-2018 Added CRC Wrapper. Extended CRC description.  01-2019 Added TIMESTAMP_LOW, TIMESTAMP_HIGH registers.  03-2019 Re-worked Prescaler. Removed 0x3 in bits 23:20 of address.  2.2 26-09-2019 Split functional descripion and register map from original document.  21-10-2019 Clarify Bus-off behaviour aftet Start-up. Clarify that frame must be inserted to TX Buffer before sending.  18-11-2019 Clarify behaviour of Transmitter delay measurement. Add notes on RX frame timestamping. Extend SSP position to 255.  13-12-2019 Clarify that only TEC above 255 will cause node to go Bus off.  304-2020 Add SETTING[PEX] and Protocol exception support.  28-10-2020 Add frame filters examples, add TBFBO and FDRF bits in SETTINGS registers, minor refactoring.  05-11-2020 Add general overview and TX frame type description.  4-2-2021 Added MODE[ROM] - Restricted operation mode.  23-2-2021 Added MODE[ROM] - Restricted operation mode.  23-2-2021 Add TXTB_INFO and mention generic number of TXT buffers.  9-4-2021 Add STATUfS[STCNT] and STATUS[STRGS] bits.  26-05-2021 Reduce maximal number of bits on the fly during secondary sampling to 4.  29-05-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer mode:  18-06-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer mode:  18-06-2021 Add MODE[TXBBM], MODE[SAM], STATUS[STRGS] is SUBJECTIONAL (STATUS) and STATUS[STRGS] bits.  26-05-2021 Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND[CTPXE], and GRAMAT_With which allow flipping of CRC or Stuff count. Add section on parity mechanism testing and starting parameters.  27-6-2022 Add SETTINOS[PCHKE] bit to control enable / disable of parity checking.  Move to new release of CTU CAN FD. Bump document version accordingly.  Add note about TXBHCfirer in MODE[TXBBM] are automatically applied to "backup" TXT Buffers. Add reset_buffer_rams and active_timestamp_bits configuration parameters.  5-7-2022 Add SETTINOS[PCHKE] bit to control enable / disable of parity checking.  Move to new release of CTU | 2.1                 | 10-2018    | Added Linux driver description                                                                                                                                                                           |

| 01-2019 Added TIMESTAMP_LOW, TIMESTAMP_HIGH registers. 03-2019 Re-worked Prescaler. Removed 0x3 in bits 23:20 of address. 2.2 26-09-2019 Split functional description and register map from original document. 21-10-2019 Clarify TXT buffer behaviour when node goes bus-off. 31-10-2019 Clarify Bus-off behaviour aftet Start-up. Clarify that frame must be inserted to TX Buffer before sending. 18-11-2019 Clarify behaviour of Transmitter delay measurement. Add notes on RX frame timestamping. Extend SSP position to 255. 13-12-2019 Clarify that only TEC above 255 will cause node to go Bus off. 30-4-2020 Add SETTING[PEX] and Protocol exception support. 28-10-2020 Add frame filters examples, add TBFBO and FDRF bits in SETTINGS registers, minor refactoring. 42-2021 Add general overview and TX frame type description. 4-2-2021 Change license 2.3 4-2-2021 Added MODE[ROM] - Restricted operation mode. 23-2-2021 Add TXTB_INFO and mention generic number of TXT buffers. 4dd RETR_CTR register. 26-4-2021 Add Add STATUS[STCNT] and STATUS[STRGS] bits. 26-05-2021 Reduce maximal number of bits on the fly during secondary sampling to 4. 29-05-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes. 11-06-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes. 24-28-08-2021 Move to new release of CTU CAN FD. Bump document version accordingly. Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRXPE]. Add remote and active_timestamp_bits configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  9-5-2021 Add Laper is Move to new release of CTU CAN FD. Bump document version accordingly. Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRXPE]. Add FRAME_FORMAT_W[ERF_FRAME_FORMAT_W[ERF_FRAME_FORMAT_W[ERF_FRAME_FORMAT_W[ERF_FRAME_FORMAT_W[ERF_FRAME_FORMAT_W[ERF_FRAME_FORMAT_W[ERF_FRAME_FORMAT_W[ERF_FRAME_FORMAT_W[ERF_FRAME_FORMAT_W[ERF_FRAME_FORMAT_W[ERF_FRAME_FORMAT_W[ERF_FRAME_FORMAT_W[ERF_FRAME |                     | 12-2018    | Added Register map block diagram after re-implementation of registers via Register map generator.                                                                                                        |

| 2.2 26-09-2019 Split functional description and register map from original document. 21-10-2019 Clarify TXT buffer behaviour when node goes bus-off. 31-10-2019 Clarify Bus-off behaviour aftet Start-up. Clarify that frame must be inserted to TX Buffer before sending.  Clarify Bus-off behaviour of Transmitter delay measurement. Add notes on RX frame timestamping. Extend SSP position to 255.  Clarify behaviour of Transmitter delay measurement. Add notes on RX frame timestamping. Extend SSP position to 255.  Clarify that only TEC above 255 will cause node to go Bus off. 30-4-2020 Add SETTING[PEX] and Protocol exception support.  Add GETTING[PEX] and Protocol exception support.  Add frame filters examples, add TBFBO and FDRF bits in SETTINGS registers, minor refactoring.  05-11-2020 Add general overview and TX frame type description.  Change license  2.3 4-2-2021 Added MODE[ROM] - Restricted operation mode.  23-2-2021 Add TXTB_INFO and mention generic number of TXT buffers.  Add RETR_CTR register.  26-4-2021 Add STATUS[STCNT] and STATUS[STRGS] bits.  26-05-2021 Reduce maximal number of bits on the fly during secondary sampling to 4.  29-05-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer model 18-06-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer model 18-06-2021 Move to new release of CTU CAN FD. Bump document version accordingly.  Add MODE[TXBBM, MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bits which allow flipping of CRC or Stuff count. Add section on parity mechanism testir configuration parameters.  Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W bits which allow flipping of CRC or Stuff count. Add section on parity mechanism testir configuration parameters.  Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_Wier. FRAME_FORMAT_Wier. Add ERR_CAPT[ERR_F] bit. Add F |                     | 12-2018    | Added CRC Wrapper. Extended CRC description.                                                                                                                                                             |

| 2.2 26-09-2019 Split functional descripion and register map from original document. 21-10-2019 Clarify TXT buffer behaviour when node goes bus-off. 31-10-2019 Clarify Bus-off behaviour aftet Start-up. Clarify that frame must be inserted to TX Buffer before sending.  18-11-2019 Clarify behaviour of Transmitter delay measurement. Add notes on RX frame timestamping. Extend SSP position to 255.  13-12-2019 Clarify that only TEC above 255 will cause node to go Bus off. 30-4-2020 Add SETTING[PEX] and Protocol exception support. 28-10-2020 Add frame filters examples, add TBFBO and FDRF bits in SETTINGS registers, minor refactoring.  05-11-2020 Add general overview and TX frame type description.  4-2-2021 Change license 2.3 4-2-2021 Add MODE[ROM] - Restricted operation mode. 23-2-2021 Add TXTB_INFO and mention generic number of TXT buffers. 4-2-2021 Add STATUS[STCNT] and STATUS[STRCS] bits. 26-0-2021 Add STATUS[STCNT] and STATUS[STRCS] bits. 26-0-2021 Reduce maximal number of bits on the fly during secondary sampling to 4. 29-05-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes. 18-06-2021 Add MODE[TTM] bit to enable time-triggered transmission. 2.4 28-08-2021 Move to new release of CTU CAN FD. Bump document version accordingly. Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bits which allow flipping of CRC or Stuff count. Add section on parity mechanism testir brackup" TXT Buffers. Add reset_buffer_rams and active_timestamp_bits configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  4-27-6-2024 Add LBPF bit to RX frame. Add MODE[RRPM]. Add FRAME_FORMAT_W bits, A |                     | 01-2019    | Added TIMESTAMP_LOW, TIMESTAMP_HIGH registers.                                                                                                                                                           |

| 21-10-2019 Clarify TXT buffer behaviour when node goes bus-off.  31-10-2019 Clarify Bus-off behaviour aftet Start-up. Clarify that frame must be inserted to TX Buffer before sending.  18-11-2019 Clarify behaviour of Transmitter delay measurement. Add notes on RX frame timestamping. Extend SSP position to 255.  13-12-2019 Clarify that only TEC above 255 will cause node to go Bus off.  30-4-2020 Add SETTING[PEX] and Protocol exception support.  28-10-2020 Add frame filters examples, add TBFBO and FDRF bits in SETTINGS registers, minor refactoring.  05-11-2020 Add general overview and TX frame type description.  4-2-2021 Change license  2.3 4-2-2021 Added MODE[ROM] - Restricted operation mode.  23-2-2021 Add RETR_CTR register.  26-4-2021 Add RATTB_INFO and mention generic number of TXT buffers.  9-4-2021 Add RATTB_INFO and mention generic number of TXT buffers.  42-2021 Add STATUS[STCNT] and STATUS[STRGS] bits.  26-0-5-2021 Reduce maximal number of bits on the fly during secondary sampling to 4.  29-05-2021 Add detailed description of disabling node by SETTINGS[ENA].  11-06-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes.  24 28-08-2021 Move to new release of CTU CAN FD. Bump document version accordingly.  Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W livit which allow dipping of CRC or Stuff count. Add section on parity mechanism testir "backup" TXT Buffers. Add reset_buffer_rams and active_timestamp_bits configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  4-2-2023 Move to new release of CTU CAN FD. Bump document version accordingly.  Add note about TXBHCl interrupt behavior.  4-2-2024 Add LBFF bit to RX frame. Add MODE[RFM, Add FRAME_FORMAT_W[ERF, FRAME_FORMAT_W[ERF, FRAME_FORMAT_W[ERF, FRAME_FORMAT_W[ERF, FRAME_FORMAT_W[ERF, Add Erro frame reception to RX buffer. Add ERR_CAPT[ERR_ERP] bit. Add FRAME_FORMAT_W[EBT] and FRAME_FORMAT_W[EBT].                                |                     | 03-2019    | Re-worked Prescaler. Removed 0x3 in bits 23:20 of address.                                                                                                                                               |

| 31-10-2019   Clarify Bus-off behaviour aftet Start-up. Clarify that frame must be inserted to TX Buffer before sending.    18-11-2019                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.2                 | 26-09-2019 | Split functional descripion and register map from original document.                                                                                                                                     |

| Buffer before sending.  Clarify behaviour of Transmitter delay measurement. Add notes on RX frame timestamping. Extend SSP position to 255.  13-12-2019 Clarify that only TEC above 255 will cause node to go Bus off.  30-4-2020 Add SETTING[PEX] and Protocol exception support.  28-10-2020 Add frame filters examples, add TBFBO and FDRF bits in SETTINGS registers, minor refactoring.  05-11-2020 Add general overview and TX frame type description.  4-2-2021 Change license  2.3 4-2-2021 Added MODE[ROM] - Restricted operation mode.  23-2-2021 Add TXTB_INFO and mention generic number of TXT buffers.  9-4-2021 Add RETR_CTR register.  26-4-2021 Add chapter about memory testability.  17-05-2021 Add STATUfS[STCNT] and STATUS[STRGS] bits.  26-05-2021 Reduce maximal number of bits on the fly during secondary sampling to 4.  29-05-2021 Add detailed description of disabling node by SETTINGS[ENA].  11-06-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes and MODE[TXBBM] and COMMAND[RXPRMV] bits, describe RX buffer modes and MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bits, which allow flipping of CRC or Stuff count. Add section on parity mechanism testing with allow flipping of CRC or Stuff count. Add section on parity mechanism testing which allow flipping of CRC or Stuff count. Add section on parity mechanism testing which allow flipping of CRC or Stuff count. Add section on parity mechanism testing which allow flipping of CRC or Stuff count. Add section on parity mechanism testing which allow flipping of CRC or Stuff count. Buffers and active_timestamp_bits configuration parameters.  - 27-6-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  4-2-2024 Add note about TXBHCI interrupt behavior.  Add LEPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERF FRAME_FORMAT_W[ERF FRAME_FORMAT_W[ERF FRAME_FORMAT_W[ERF FRAME_FORMAT_W[ERF FRAME_F |                     | 21-10-2019 | Clarify TXT buffer behaviour when node goes bus-off.                                                                                                                                                     |

| 18-11-2019 Clarify behaviour of Transmitter delay measurement. Add notes on RX frame timestamping. Extend SSP position to 255.  13-12-2019 Clarify that only TEC above 255 will cause node to go Bus off. 30-4-2020 Add SETTING[PEX] and Protocol exception support.  28-10-2020 Add frame filters examples, add TBFBO and FDRF bits in SETTINGS registers, minor refactoring.  05-11-2020 Add general overview and TX frame type description. 4-2-2021 Change license 2.3 4-2-2021 Added MODE[ROM] - Restricted operation mode. 23-2-2021 Add TXTB_INFO and mention generic number of TXT buffers. 9-4-2021 Add RETR_CTR register. 26-4-2021 Add STATUfS[STCNT] and STATUS[STRGS] bits. 17-05-2021 Add STATUfS[STCNT] and STATUS[STRGS] bits. 26-05-2021 Reduce maximal number of bits on the fly during secondary sampling to 4. 29-05-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes 18-06-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes 18-06-2021 Add MODE[TTTM] bit to enable time-triggered transmission. 2.4 28-08-2021 Move to new release of CTU CAN FD. Bump document version accordingly. Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bit which allow flipping of CRC or Stuff count. Add section on parity mechanism testin "backup" TXT Buffers. Add reset_buffer_rams and active_timestamp_bits configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking. 4-2-2024 Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERF FRAME_FO |                     | 31-10-2019 | Clarify Bus-off behaviour aftet Start-up. Clarify that frame must be inserted to TXT                                                                                                                     |

| timestamping. Extend SSP position to 255.  13-12-2019 Clarify that only TEC above 255 will cause node to go Bus off. 30-4-2020 Add SETTING[PEX] and Protocol exception support.  28-10-2020 Add frame filters examples, add TBFBO and FDRF bits in SETTINGS registers, minor refactoring.  05-11-2020 Add general overview and TX frame type description. 4-2-2021 Change license 2.3 4-2-2021 Added MODE[ROM] - Restricted operation mode. 23-2-2021 Add TXTB_INFO and mention generic number of TXT buffers. 9-4-2021 Add TXTB_INFO and mention generic number of TXT buffers. 4dd chapter about memory testability. 17-05-2021 Add STATU/S[STCNT] and STATUS[STRGS] bits. 26-05-2021 Reduce maximal number of bits on the fly during secondary sampling to 4. 29-05-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes. 18-06-2021 Add MODE[RTIM] bit to enable time-triggered transmission. 2.4 28-08-2021 Move to new release of CTU CAN FD. Bump document version accordingly. 1-4-2022 Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bits which allow flipping of CRC or Stuff count. Add section on parity mechanism testin shackup." TXT Buffers. Add reset_buffer_rams and active_timestamp_bits configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking. 4-2-2024 Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERF FRAME_F |                     |            | Buffer before sending.                                                                                                                                                                                   |

| 13-12-2019 Clarify that only TEC above 255 will cause node to go Bus off.  30-4-2020 Add SETTING[PEX] and Protocol exception support.  28-10-2020 Add frame filters examples, add TBFBO and FDRF bits in SETTINGS registers, minor refactoring.  05-11-2020 Add general overview and TX frame type description.  4-2-2021 Change license  2.3 4-2-2021 Added MODE[ROM] - Restricted operation mode.  23-2-2021 Add TXTB_INFO and mention generic number of TXT buffers.  9-4-2021 Add STATUFS[STCNT] and STATUS[STRGS] bits.  17-05-2021 Add STATUFS[STCNT] and STATUS[STRGS] bits.  26-05-2021 Reduce maximal number of bits on the fly during secondary sampling to 4.  29-05-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes and MODE[TTM] bit to enable time-triggered transmission.  2.4 28-08-2021 Move to new release of CTU CAN FD. Bump document version accordingly.  Add MODE[TXBBM], MODE[SAM], STATUS[XPKE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bits which allow flipping of CRC or Stuff count. Add section on parity mechanism testin Succonfiguration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  4dd LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERFF FRAME_FORMAT_W[ERF FRAME_FORMAT_W[ENF FRAME_FORMAT |                     | 18-11-2019 | Clarify behaviour of Transmitter delay measurement. Add notes on RX frame                                                                                                                                |

| 30-4-2020 Add SETTING[PEX] and Protocol exception support.  28-10-2020 Add frame filters examples, add TBFBO and FDRF bits in SETTINGS registers, minor refactoring.  05-11-2020 Add general overview and TX frame type description.  4-2-2021 Change license  2.3 4-2-2021 Added MODE[ROM] - Restricted operation mode.  23-2-2021 Add TXTB_INFO and mention generic number of TXT buffers.  9-4-2021 Add RETR_CTR register.  26-4-2021 Add STATUfS[STCNT] and STATUS[STRGS] bits.  17-05-2021 Add STATUfS[STCNT] and STATUS[STRGS] bits.  26-05-2021 Reduce maximal number of bits on the fly during secondary sampling to 4.  29-05-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes and MODE[TXBM] and COMMAND[RXRPMV] bits, describe RX buffer modes and MODE[TXBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bit which allow flipping of CRC or Stuff count. Add section on parity mechanism testing which allow flipping of CRC or Stuff count. Add section on parity mechanism testing configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  5-7-2023 Move to new release of CTU CAN FD. Bump document version accordingly.  Add reset_buffer_rams and active_timestamp_bits configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  4dd note about TXBHCI interrupt behavior.  Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERF FRAME_FORMAT_W[ERF *]]. Add Error frame reception to RX buffer. Add ERR_CAPT[ERR_ERP] bit. Add FRAME_FORMAT_W[ERF *] bit. Add FRAME_FORMAT_W[ERF *] bit. Add FRAME_FORMAT_W[LBTBI] and FRAME_FORMAT_W[LBTBI] and FRAME_FORMAT_W[LBTBI] and FRAME_FORMAT_W[UVLD].                                                                                                                                                                                                                                                                                                              |                     |            | timestamping. Extend SSP position to 255.                                                                                                                                                                |

| 28-10-2020 Add frame filters examples, add TBFBO and FDRF bits in SETTINGS registers, minor refactoring.  05-11-2020 Add general overview and TX frame type description.  4-2-2021 Change license  2.3 4-2-2021 Added MODE[ROM] - Restricted operation mode.  23-2-2021 Add RETR_CTR register.  9-4-2021 Add RETR_CTR register.  26-4-2021 Add STATUFS[STCNT] and STATUS[STRGS] bits.  26-05-2021 Reduce maximal number of bits on the fly during secondary sampling to 4.  29-05-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes and MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes and MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes and MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes and MODE[RXBAM] and COMMAND[CRYED], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE], Add FRAME_FORMAT_W bit which allow flipping of CRC or Stuff count. Add section on parity mechanism testing which allow flipping of CRC or Stuff count. Add section on parity mechanism testing "backup" TXT Buffers. Add reset_buffer_amms and active_timestamp_bits configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  9-12-2023 Move to new release of CTU CAN FD. Bump document version accordingly.  Add note about TXBHCI interrupt behavior.  Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT]]. Add ERR_CAPT[ERR_ERP] bit. Add FRAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT]]. Add ERR_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT]]. Add ERRAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ER |                     | 13-12-2019 | Clarify that only TEC above 255 will cause node to go Bus off.                                                                                                                                           |

| minor refactoring.  05-11-2020 Add general overview and TX frame type description.  4-2-2021 Change license  2.3 4-2-2021 Added MODE[ROM] - Restricted operation mode.  23-2-2021 Add TXTB_INFO and mention generic number of TXT buffers.  9-4-2021 Add RETR_CTR register.  26-4-2021 Add chapter about memory testability.  17-05-2021 Add STATUfS[STCNT] and STATUS[STRGS] bits.  26-05-2021 Reduce maximal number of bits on the fly during secondary sampling to 4.  29-05-2021 Add detailed description of disabling node by SETTINGS[ENA].  11-06-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes and MODE[TTTM] bit to enable time-triggered transmission.  2.4 28-08-2021 Move to new release of CTU CAN FD. Bump document version accordingly.  1-4-2022 Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bits which allow flipping of CRC or Stuff count. Add section on parity mechanism testin "backup" TXT Buffers. Add reset_buffer_rams and active_timestamp_bits configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  5-7-2024 Add note about TXBHCI interrupt behavior.  Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERF FRAME_FOR |                     | 30-4-2020  | Add SETTING[PEX] and Protocol exception support.                                                                                                                                                         |

| O5-11-2020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     | 28-10-2020 | Add frame filters examples, add TBFBO and FDRF bits in SETTINGS registers,                                                                                                                               |

| 4-2-2021 Added MODE[ROM] - Restricted operation mode.  23-2-2021 Add TXTB_INFO and mention generic number of TXT buffers.  9-4-2021 Add Chapter about memory testability.  17-05-2021 Add STATUS[STCNT] and STATUS[STRGS] bits.  26-05-2021 Reduce maximal number of bits on the fly during secondary sampling to 4.  29-05-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes.  18-06-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes.  18-06-2021 Add MODE[TTTM] bit to enable time-triggered transmission.  2.4 28-08-2021 Move to new release of CTU CAN FD. Bump document version accordingly.  1-4-2022 Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bits which allow flipping of CRC or Stuff count. Add section on parity mechanism testing the section of the section |                     |            | minor refactoring.                                                                                                                                                                                       |

| 2.3 4-2-2021 Added MODE[ROM] - Restricted operation mode.  23-2-2021 Add TXTB_INFO and mention generic number of TXT buffers.  9-4-2021 Add RETR_CTR register.  26-4-2021 Add chapter about memory testability.  17-05-2021 Add STATUfS[STCNT] and STATUS[STRGS] bits.  26-05-2021 Reduce maximal number of bits on the fly during secondary sampling to 4.  29-05-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes 18-06-2021 Add MODE[TTTM] bit to enable time-triggered transmission.  2.4 28-08-2021 Move to new release of CTU CAN FD. Bump document version accordingly.  1-4-2022 Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bit which allow flipping of CRC or Stuff count. Add section on parity mechanism testin "backup" TXT Buffers. Add reset_buffer_rams and active_timestamp_bits configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  Move to new release of CTU CAN FD. Bump document version accordingly.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  Move to new release of CTU CAN FD. Bump document version accordingly.  4 Add note about TXBHCI interrupt behavior.  19-6-2024 Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERF FRAME_FORMAT_W[ERF *]]. Add Error frame reception to RX buffer. Add ERR_CAPT[ERR_ERP] bit. Add FRAME_FORMAT_W[ERF] and FRAME_FORMAT_W[ERF *]]. Add FRAME_FORMAT_W[ERF] and FRAME_FORMAT_W[ERF].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     | 05-11-2020 | Add general overview and TX frame type description.                                                                                                                                                      |

| 23-2-2021 Add TXTB_INFO and mention generic number of TXT buffers.  9-4-2021 Add RETR_CTR register.  26-4-2021 Add chapter about memory testability.  17-05-2021 Add STATUfS[STCNT] and STATUS[STRGS] bits.  26-05-2021 Reduce maximal number of bits on the fly during secondary sampling to 4.  29-05-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes.  18-06-2021 Add MODE[TTTM] bit to enable time-triggered transmission.  2.4 28-08-2021 Move to new release of CTU CAN FD. Bump document version accordingly.  1-4-2022 Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bit which allow flipping of CRC or Stuff count. Add section on parity mechanism testing.  - 27-6-2022 SW commands on TXT Buffers in MODE[TXBBM] are automatically applied to "backup" TXT Buffers. Add reset_buffer_rams and active_timestamp_bits configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  2.5 9-12-2023 Move to new release of CTU CAN FD. Bump document version accordingly.  Add note about TXBHCI interrupt behavior.  Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERF FRAME_FORMAT_W[ERF.*]. Add Error frame reception to RX buffer. Add ERR_CAPT[ERR_ERP] bit. Add FRAME_FORMAT_W[LBTBI] and FRAME_FORMAT_W[ULD].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                     | 4-2-2021   | Change license                                                                                                                                                                                           |

| 9-4-2021 Add RETR_CTR register.  26-4-2021 Add chapter about memory testability.  17-05-2021 Add STATUfS[STCNT] and STATUS[STRGS] bits.  26-05-2021 Reduce maximal number of bits on the fly during secondary sampling to 4.  29-05-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes.  11-06-2021 Add MODE[TTTM] bit to enable time-triggered transmission.  2.4 28-08-2021 Move to new release of CTU CAN FD. Bump document version accordingly.  1-4-2022 Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bit which allow flipping of CRC or Stuff count. Add section on parity mechanism testin "backup" TXT Buffers. Add reset_buffer_rams and active_timestamp_bits configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  2.5 9-12-2023 Move to new release of CTU CAN FD. Bump document version accordingly.  Add note about TXBHCI interrupt behavior.  4 Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERF_FRAME_FORMAT_W[ERF_*]. Add Error frame reception to RX buffer. Add ERR_CAPT[ERR_ERP] bit. Add FRAME_FORMAT_W[LBTBI] and FRAME_FORMAT_W[UVLD].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.3                 | 4-2-2021   | Added MODE[ROM] - Restricted operation mode.                                                                                                                                                             |

| 26-4-2021 Add chapter about memory testability.  17-05-2021 Add STATUfS[STCNT] and STATUS[STRGS] bits.  26-05-2021 Reduce maximal number of bits on the fly during secondary sampling to 4.  29-05-2021 Add detailed description of disabling node by SETTINGS[ENA].  11-06-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes 18-06-2021 Add MODE[TTTM] bit to enable time-triggered transmission.  2.4 28-08-2021 Move to new release of CTU CAN FD. Bump document version accordingly.  1-4-2022 Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bit which allow flipping of CRC or Stuff count. Add section on parity mechanism testin which allow flipping of CRC or Stuff count. Add section on parity mechanism testin configuration parameters.  27-6-2022 SW commands on TXT Buffers in MODE[TXBBM] are automatically applied to "backup" TXT Buffers. Add reset_buffer_rams and active_timestamp_bits configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  2.5 9-12-2023 Move to new release of CTU CAN FD. Bump document version accordingly.  8-5-2024 Add note about TXBHCI interrupt behavior.  19-6-2024 Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERF FRAME_FORMAT_W[ERF * ]. Add Error frame reception to RX buffer. Add ERR_CAPT[ERR_ERP] bit. Add FRAME_FORMAT_W[LBTBI] and FRAME_FORMAT_W[L |                     | 23-2-2021  | Add TXTB_INFO and mention generic number of TXT buffers.                                                                                                                                                 |

| 17-05-2021 Add STATUfS[STCNT] and STATUS[STRGS] bits.  26-05-2021 Reduce maximal number of bits on the fly during secondary sampling to 4.  29-05-2021 Add detailed description of disabling node by SETTINGS[ENA].  11-06-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes 18-06-2021 Add MODE[TTTM] bit to enable time-triggered transmission.  2.4 28-08-2021 Move to new release of CTU CAN FD. Bump document version accordingly.  1-4-2022 Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bit which allow flipping of CRC or Stuff count. Add section on parity mechanism testin "Sw commands on TXT Buffers in MODE[TXBBM] are automatically applied to "backup" TXT Buffers. Add reset_buffer_rams and active_timestamp_bits configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  2.5 9-12-2023 Move to new release of CTU CAN FD. Bump document version accordingly.  3-5-2024 Add note about TXBHCI interrupt behavior.  4dd LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERFF FRAME_FORMAT_W[ERFF *]. Add Error frame reception to RX buffer. Add ERR_CAPT[ERR_ERP] bit. Add FRAME_FORMAT_W[LBTBI] and FRAME_FORMAT_W[UVLD].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                     | 9-4-2021   | Add RETR_CTR register.                                                                                                                                                                                   |

| 26-05-2021 Reduce maximal number of bits on the fly during secondary sampling to 4. 29-05-2021 Add detailed description of disabling node by SETTINGS[ENA].  11-06-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes 18-06-2021 Add MODE[TTTM] bit to enable time-triggered transmission.  2.4 28-08-2021 Move to new release of CTU CAN FD. Bump document version accordingly.  1-4-2022 Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bit which allow flipping of CRC or Stuff count. Add section on parity mechanism testin "backup" TXT Buffers. Add reset_buffer_rams and active_timestamp_bits configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  2.5 9-12-2023 Move to new release of CTU CAN FD. Bump document version accordingly.  Add note about TXBHCI interrupt behavior.  19-6-2024 Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERFF FRAME_FORMAT_W[ERFF_*]. Add FRAME_FORMAT_W[ERFF Add ERR_CAPT[ERR_ERP] bit. Add FRAME_FORMAT_W[LBTBI] and FRAME_FORMAT_W[UVLD].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                     | 26-4-2021  | Add chapter about memory testability.                                                                                                                                                                    |

| 29-05-2021 Add detailed description of disabling node by SETTINGS[ENA].  11-06-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes 18-06-2021 Add MODE[TTTM] bit to enable time-triggered transmission.  2.4 28-08-2021 Move to new release of CTU CAN FD. Bump document version accordingly.  1-4-2022 Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bit which allow flipping of CRC or Stuff count. Add section on parity mechanism testin SW commands on TXT Buffers in MODE[TXBBM] are automatically applied to "backup" TXT Buffers. Add reset_buffer_rams and active_timestamp_bits configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  2.5 9-12-2023 Move to new release of CTU CAN FD. Bump document version accordingly.  8-5-2024 Add note about TXBHCI interrupt behavior.  19-6-2024 Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERFFRAME_FORMAT_W[ERFF_*]]. Add Error frame reception to RX buffer. Add ERR_CAPT[ERR_ERP] bit. Add FRAME_FORMAT_W[LBTBI] and FRAME_FORMAT_W[UVLD].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     | 17-05-2021 | Add STATUfS[STCNT] and STATUS[STRGS] bits.                                                                                                                                                               |

| 11-06-2021 Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes 18-06-2021 Add MODE[TTTM] bit to enable time-triggered transmission.  2.4 28-08-2021 Move to new release of CTU CAN FD. Bump document version accordingly.  1-4-2022 Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bit which allow flipping of CRC or Stuff count. Add section on parity mechanism testir  27-6-2022 SW commands on TXT Buffers in MODE[TXBBM] are automatically applied to "backup" TXT Buffers. Add reset_buffer_rams and active_timestamp_bits configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  9-12-2023 Move to new release of CTU CAN FD. Bump document version accordingly.  Add note about TXBHCI interrupt behavior.  19-6-2024 Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERF FRAME_FORMAT_W[ERF_*]. Add Error frame reception to RX buffer. Add ERR_CAPT[ERR_ERP] bit. Add FRAME_FORMAT_W[LBTBI] and FRAME_FORMAT_W[VLD].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                     | 26-05-2021 | Reduce maximal number of bits on the fly during secondary sampling to 4.                                                                                                                                 |

| 18-06-2021 Add MODE[TTTM] bit to enable time-triggered transmission.  2.4 28-08-2021 Move to new release of CTU CAN FD. Bump document version accordingly.  1-4-2022 Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bit which allow flipping of CRC or Stuff count. Add section on parity mechanism testir  27-6-2022 SW commands on TXT Buffers in MODE[TXBBM] are automatically applied to "backup" TXT Buffers. Add reset_buffer_rams and active_timestamp_bits configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  9-12-2023 Move to new release of CTU CAN FD. Bump document version accordingly.  Add note about TXBHCI interrupt behavior.  19-6-2024 Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[LBTBI]] and FRAME_FORMAT_W[VIVLD].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                     | 29-05-2021 | Add detailed description of disabling node by SETTINGS[ENA].                                                                                                                                             |

| 2.4 28-08-2021 Move to new release of CTU CAN FD. Bump document version accordingly.  1-4-2022 Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bit which allow flipping of CRC or Stuff count. Add section on parity mechanism testin  - 27-6-2022 SW commands on TXT Buffers in MODE[TXBBM] are automatically applied to "backup" TXT Buffers. Add reset_buffer_rams and active_timestamp_bits configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  2.5 9-12-2023 Move to new release of CTU CAN FD. Bump document version accordingly.  8-5-2024 Add note about TXBHCI interrupt behavior.  19-6-2024 Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[LBTBI]] and FRAME_FORMAT_W[LBTBI] and FRAME_FORMAT_W[UVLD].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     | 11-06-2021 | Add MODE[RXBAM] and COMMAND[RXRPMV] bits, describe RX buffer modes.                                                                                                                                      |

| 1-4-2022 Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bit which allow flipping of CRC or Stuff count. Add section on parity mechanism testin  - 27-6-2022 SW commands on TXT Buffers in MODE[TXBBM] are automatically applied to "backup" TXT Buffers. Add *reset_buffer_rams* and *active_timestamp_bits* configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  2.5 9-12-2023 Move to new release of CTU CAN FD. Bump document version accordingly.  8-5-2024 Add note about TXBHCI interrupt behavior.  19-6-2024 Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[ERFFAME_FORMAT_W[LBTBI]] and FRAME_FORMAT_W[LBTBI] and FRAME_FORMAT_W[LBTBI] and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                     | 18-06-2021 | Add MODE[TTTM] bit to enable time-triggered transmission.                                                                                                                                                |

| COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bit which allow flipping of CRC or Stuff count. Add section on parity mechanism testing.  27-6-2022 SW commands on TXT Buffers in MODE[TXBBM] are automatically applied to "backup" TXT Buffers. Add reset_buffer_rams and active_timestamp_bits configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  2.5 9-12-2023 Move to new release of CTU CAN FD. Bump document version accordingly.  8-5-2024 Add note about TXBHCI interrupt behavior.  19-6-2024 Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERFFRAME_FORMAT_W[ERFFRAME_FORMAT_W[ERFFRAME_FORMAT_W[ERFFRAME_FORMAT_W[LBTBI]] and FRAME_FORMAT_W[LBTBI] and FRAME_FORMAT_W[UVLD].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.4                 | 28-08-2021 | Move to new release of CTU CAN FD. Bump document version accordingly.                                                                                                                                    |

| - 27-6-2022 SW commands on TXT Buffers in MODE[TXBBM] are automatically applied to "backup" TXT Buffers. Add reset_buffer_rams and active_timestamp_bits configuration parameters.  5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  2.5 9-12-2023 Move to new release of CTU CAN FD. Bump document version accordingly.  8-5-2024 Add note about TXBHCI interrupt behavior.  19-6-2024 Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERFFAME_FORMAT_W[ERF_*]. Add Error frame reception to RX buffer. Add ERR_CAPT[ERR_ERP] bit. Add FRAME_FORMAT_W[LBTBI] and FRAME_FORMAT_W[VLD].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                     | 1-4-2022   | Add MODE[TXBBM], MODE[SAM], STATUS[RXPE], STATUS[TXPE], COMMAND [CTPXE] and COMMAND[CRPXE]. Add FRAME_FORMAT_W bits which allow flipping of CRC or Stuff count. Add section on parity mechanism testing. |

| 5-7-2022 Add SETTINGS[PCHKE] bit to control enable / disable of parity checking.  9-12-2023 Move to new release of CTU CAN FD. Bump document version accordingly.  8-5-2024 Add note about TXBHCI interrupt behavior.  19-6-2024 Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERFFAME_FORMAT_W[ERF_*]. Add Error frame reception to RX buffer. Add ERR_CAPT[ERR_ERP] bit. Add FRAME_FORMAT_W[LBTBI] and FRAME_FORMAT_W[IVLD].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                   | 27-6-2022  | SW commands on TXT Buffers in MODE[TXBBM] are automatically applied to "backup" TXT Buffers. Add <i>reset_buffer_rams</i> and <i>active_timestamp_bits</i>                                               |

| 2.5 9-12-2023 Move to new release of CTU CAN FD. Bump document version accordingly.  8-5-2024 Add note about TXBHCI interrupt behavior.  19-6-2024 Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERFFAME_FORMAT_W[ERF_*]. Add Error frame reception to RX buffer. Add ERR_CAPT[ERR_ERP] bit. Add FRAME_FORMAT_W[LBTBI] and FRAME_FORMAT_W[IVLD].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     | F 7 2022   | - ·                                                                                                                                                                                                      |

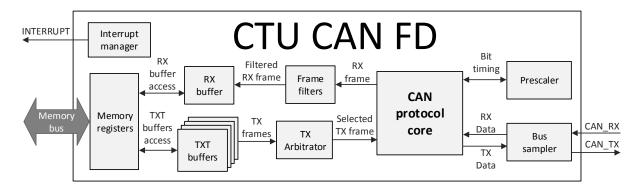

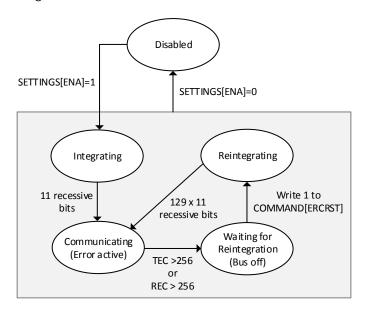

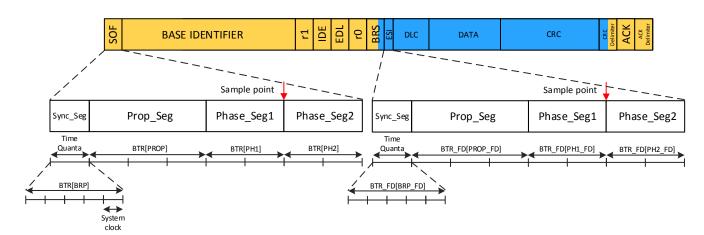

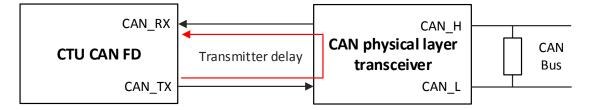

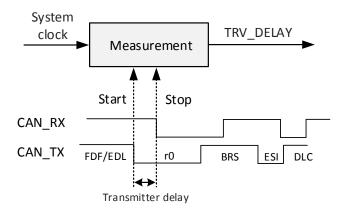

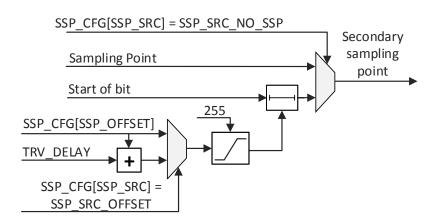

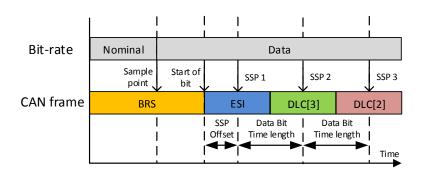

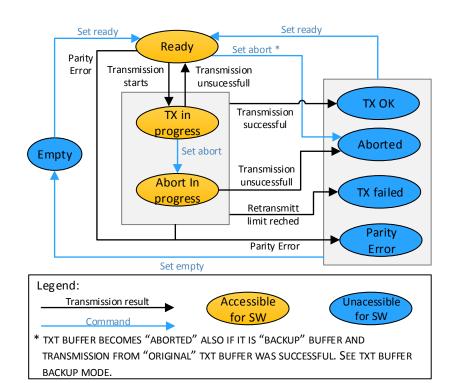

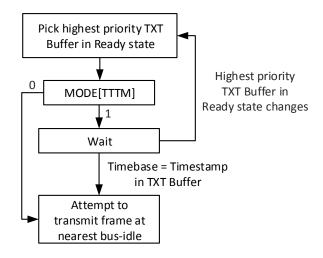

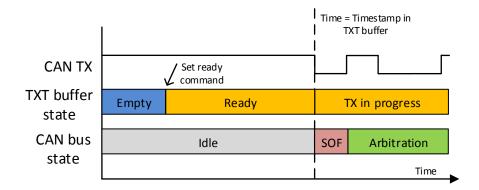

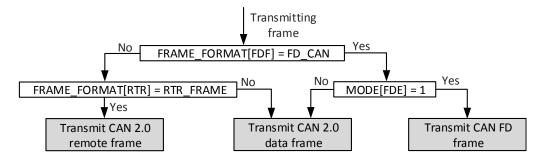

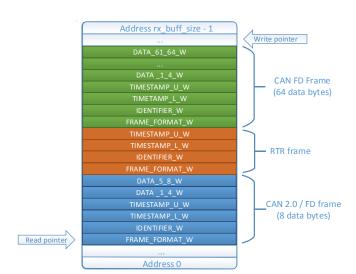

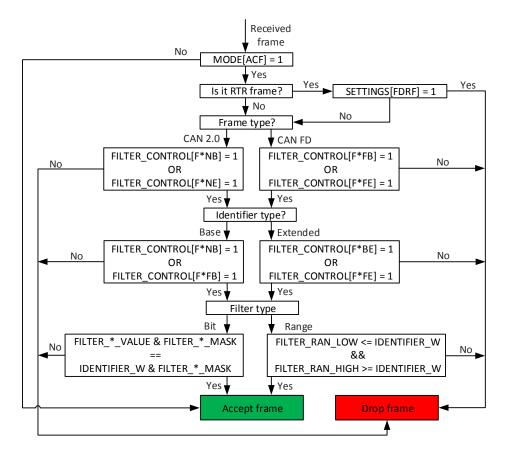

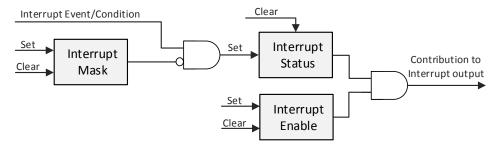

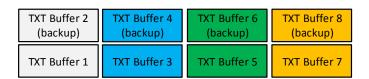

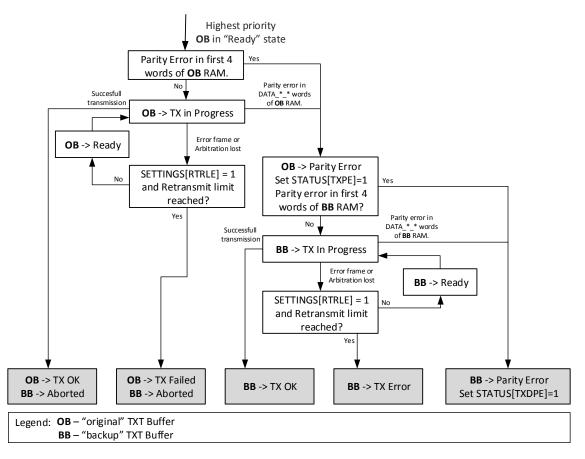

| 8-5-2024 Add note about TXBHCI interrupt behavior.  19-6-2024 Add LBPF bit to RX frame. Add MODE[ERFM]. Add FRAME_FORMAT_W[ERF FRAME_FORMAT_W[ERF_*]. Add Error frame reception to RX buffer. Add ERR_CAPT[ERR_ERP] bit. Add FRAME_FORMAT_W[LBTBI] and FRAME_FORMAT_W[IVLD].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.5                 |            |                                                                                                                                                                                                          |